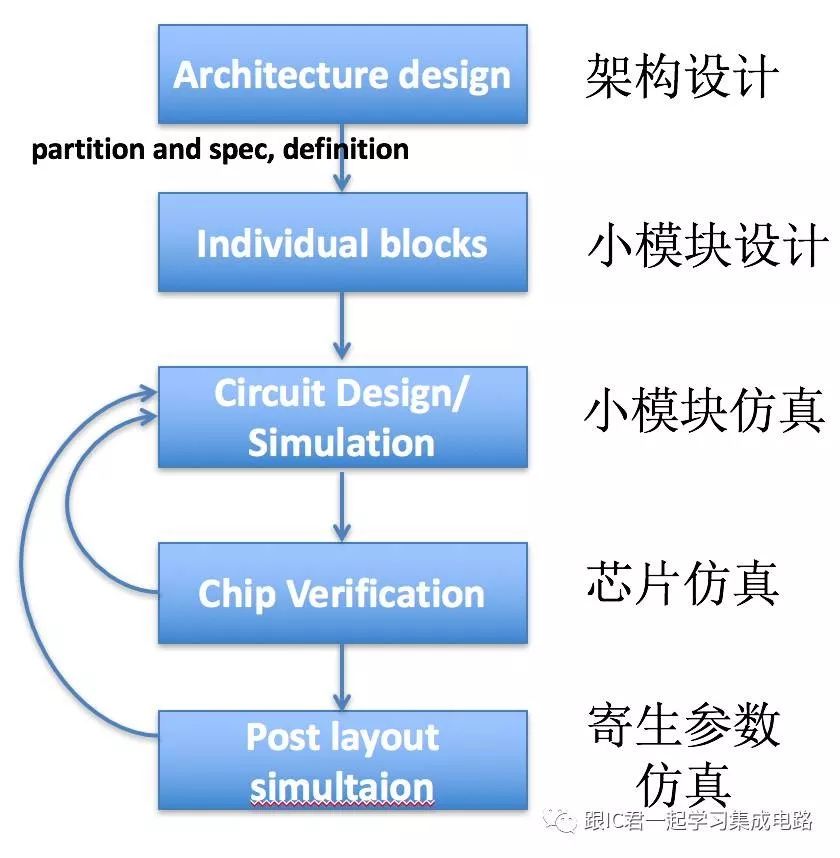

In the course of this project, IC Jun has been reflecting on why most of the projects have been busy since working for 7 years. Always busy with tapeout? Why do some projects fail? "Poor Charlie Collection" Buffett’s partner Charlie Munger thinks everything should be reversed: To make a successful project, the first is to study how to make a "failed" IC project. The failure of the definition here means that the process of project implementation is very confusing and that everyone has worked hard. However, there are a lot of bugs that come out of the chip at the end, and they may not work at all. As for the production of chips, the inaccurate positioning of the market, the difficulty in selling, or the making of profits are not among our discussions. The project flow of our IC is often as follows: The classification of the steps in this figure is rather crude, and the functions of the specific parts of the previous article also said that the new skills of the IC engineers - digital and analog mixed articles. A more detailed process can refer to the previous article as a front-end digital IC engineer's day. Here are some steps to explore how to make a "failed" project. 1 Architecture design determines the function and design division of a chip. It is the most important part, and it determines the future direction of our efforts. If the direction of effort is wrong, the more you do, the more mistakes you make! To make the project fail, this step is the easiest. For example, during the execution of the project, the architecture is constantly changing, but the date of tapeout has not changed: Originally wanted to do high-speed chips, suddenly want to do the lowest power consumption; At first I wanted to make a very small chip, and later it became a large chip, adding numerous features during the process. The features added before tapeout are the most problematic! The risk of a moderate module is not fully assessed at the beginning, so that more and more bugs are discovered. If you completely need to change a lot of blocks, you can only tinker; The understanding of the spec was wrong, the problem was discovered in the middle and later stages of project implementation, and many circuits were needed to implement the correct spec; Did not correctly assess the feasibility of the package, such as doing behind the sudden discovery of 8SOP package does not go in, pad position needs to be changed, many of the assessment done before done completely. The architecture design is mainly done under the lead of the project leader. Of course, some things are not completely decided by the leader. The boss often participates in it. Sometimes the change in the architecture is caused by the market, and a decisive change of structure may be a correct decision for the company. For example, with the rise of wearable products for a certain period of time, low-power consumption has suddenly become a characteristic that everyone urgently needs, and it is not so care for speed. Changes to the architecture For IC engineers, they can only accept and make more simulations to ensure that the architecture changes are OK. Whatever the reason, frequent changes to the architecture are the most likely causes of project failure! 2 The design and simulation verification of the small module is the work content of the vast number of IC engineers, do their own part of the responsibility. For a failed project, the hazard of this step is much smaller than the architecture design. If you want to fail the project, you can do this by: The responsible module, after assessing itself, found that the workload was huge or extremely difficult, but he hoped to complete it through his own efforts, silently doing for months without timely highlighting these issues to the leader; In the absence of clear circuit function, modify the circuit of the inherited item. How did the previous project be so stupid? No, I have to change it and let it have a smaller number of gates and a smaller area! I didn't want to be clear about all kinds of unexpected cases when implementing the function, but simply implemented the function of spec; There is no enough margin left for the timing check. It is easy to make mistakes in the post layout simulation. Some modules may have to run all the craft corners. When actually doing, only one TT process is run. It is impossible to run all the processes during the subsequent chip-level verification. It is possible that the chip technology will not work properly with a slight drift. For example, you did an RC delay is 5ns under the TT process, but the process floats to 15ns, and the circuit may fail; There is no redundancy in the design, and we think we will minimize the area. Tapeout does not have a gate for you to use when modifying the circuit. This is also a mistake that IC Jun is easy to make. Does not comply with some of the established design rules. For example, when the circuit is integrated, latches are not expected and the specific RTL code must be followed. 3 Chip simulation is the simulation verification that includes all modules. After the integration, you will find many problems that are not considered when designing small modules. There are usually many engineers involved in this step, so many of the problems in the previous step can be covered here, and it seems not so easy for the project to fail. The simulation environment and the actual working environment of the circuit are not matched. Without dspf, there is no parasitic effect. It seems that the work is good and stickout comes out; The behavior model is written incorrectly. The simulation behavior you see is inconsistent with the actual chip. The verification result is perfect and the actual result cannot be seen. This harm is really big; Because the chip simulation is also responsible for different people, if the person in charge does not verify some of the check in accordance with the established flow and misses a lot of cases, it increases the probability of failure; The person responsible for the check is not very experienced, even if you see the wrong simulation results still can not find the problem; The simulation time is very long, and there is no method to increase the simulation speed. It takes a long time to perform a simulation. When you simulate the results, the daylily is cool. How to avoid this problem can refer to our previous article How to reduce the simulation time for IC design and verification. 4 Parasitic simulation (post-layout simulation) is a simulation that takes into account the actual layout extraction of parasitic parameters. This step is usually the same as the second step. If the project fails, it may be due to the following reasons: There is no simulation of parasitic parameters at all. The node of the circuit has no parasitic RC at all. The simulation results look particularly good, but the layout may have taken a long metal line. It is possible that the setup time is illegal. Improper use of tools for extracting parasitic parameters: For example, using calibre's tools to extract parasitic parameters, there are many options to set. It is possible that the extraction of parasitic results is either too heavy or too light compared to the actual layout, resulting in incorrect simulation results; No layout checking is done. Some modules require special layouts such as current mirrors, bandgap, amplifiers, etc.; there are special traces (special line widths) and layout checks are also needed to ensure that the version of tapeout matches your simulated version. Consistent. 5 Other reasons are mainly related to some factory-related issues. Previous articles also mentioned that some talked about the failure of tapeout. These problems are usually very serious, a fatal type: The mask has given you an error. There is less of a layer or a previous version. Some devices are used well and suddenly I suggest you do not use it; The factory's capacity is not enough, need to change the process or change the factory. Circuits directly connected to PAD do not consider ESD issues Each company may have a tapeout checklist. Tapeout does not check these rules before, and it is likely to fail. I just want to know where I will die in the future so that I will not go there. Due to the limited personal knowledge, the reasons for the failure of some projects are listed above. We can also post messages in WeChat articles or knowing articles. IC Jun will revise and supplement articles. Finally, we hope that everyone will not make these mistakes during the implementation of the project.

ZGAR GenkiIppai Pods 5.0

ZGAR electronic cigarette uses high-tech R&D, food grade disposable pod device and high-quality raw material. All package designs are Original IP. Our designer team is from Hong Kong. We have very high requirements for product quality, flavors taste and packaging design. The E-liquid is imported, materials are food grade, and assembly plant is medical-grade dust-free workshops.

From production to packaging, the whole system of tracking, efficient and orderly process, achieving daily efficient output. WEIKA pays attention to the details of each process control. The first class dust-free production workshop has passed the GMP food and drug production standard certification, ensuring quality and safety. We choose the products with a traceability system, which can not only effectively track and trace all kinds of data, but also ensure good product quality.

We offer best price, high quality Pods, Pods Touch Screen, Empty Pod System, Pod Vape, Disposable Pod device, E-cigar, Vape Pods to all over the world.

Much Better Vaping Experience!

ZGAR GenkiIppai 5.0 Pods,ZGAR GenkiIppai Pods 5.0,ZGAR GenkiIppai Pods 5.0 Pod System Vape,ZGAR GenkiIppai Pods 5.0 Disposable Pod Vape Systems, Japanese culture style Zgar International (M) SDN BHD , https://www.szvape-pen.com