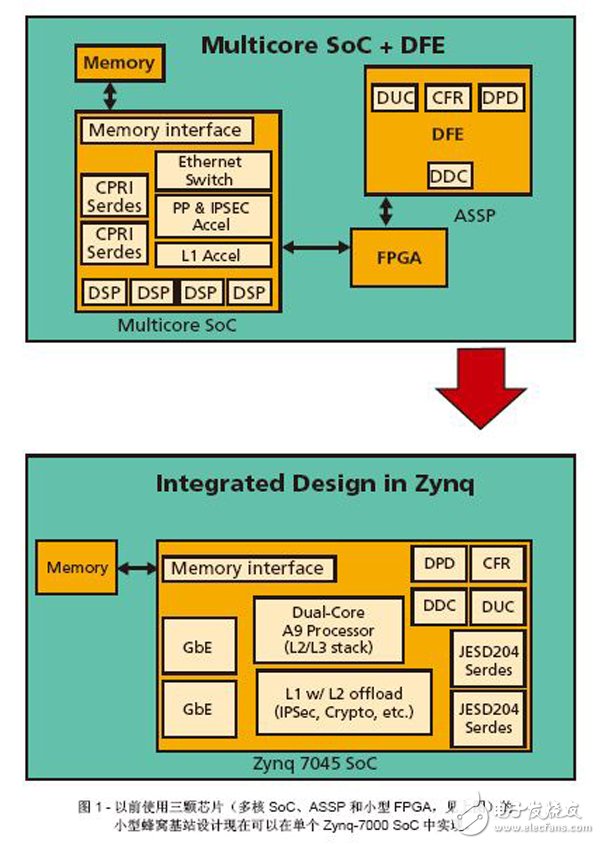

The Xilinx Zynq-7000 All Programmalbe SoC enables new levels of integration, flexibility and low power consumption in femto, pico and other small cell base station designs. Small cells are low-power wireless base stations that operate within the licensed spectrum and are managed by mobile network operators. The types of small cell base stations include femtocells, picocells, microcells, and multicell base stations (Metrocells) ranging from one hundred meters to hundreds of meters. Today, the electronic core components of small cell systems include FPGAs, DSP devices, and network and host processors that meet the evolving wireless standards. However, a new generation of small cellular systems is rapidly and highly integrated, integrating these components into a single system-on-a-chip (SoC). Telecom operators can use small cells to expand the coverage and capacity of cellular networks in homes, businesses, and urban and rural public spaces. Whether at home or at work, more and more customers want to use their mobile phones anytime, anywhere, even with fixed networks. In addition, they also want coverage to be ubiquitous and enjoy innovative mobile data services with sufficient bandwidth. Most and more and more data usage occurs indoors, but macrocells have poor coverage indoors. Therefore, small cells can play an important role in bridging coverage and capacity requirements. Small cells not only reduce the number of disconnections, increase data rates, improve end-user experience, but also reduce capital and operating expenses for operators, thereby reducing site rental, maintenance, and electricity costs. The Xilinx Zynq®-7000 All Programmable SoC combines the software programmability of a processor with the hardware programmability of an FPGA to deliver unparalleled system performance, flexibility and scalability while reducing power consumption. Significant system advantages have been achieved in terms of cost reduction and speeding up the listing process. Thanks to its soft/hard programmable functionality, the Zynq SoC offers customers unparalleled programmable features and differentiation capabilities compared to traditional SoC processing solutions. Standard SoCs are only software programmable, greatly limiting design flexibility and differentiation, and are not conducive to effectively adapting to evolving wireless standards. ZYNQ SoC is ideal for LTE small cell base stations Many small cellular base stations must operate without a cooling fan, thus placing high demands on heat dissipation. The Zynq SoC's low power consumption not only eliminates the need for fans in the system, it also eliminates the need to install expensive heat sinks. Many small cellular base stations must operate without a cooling fan, thus placing high demands on heat dissipation. The Zynq SoC's low power consumption not only eliminates the need for fans in the system, it also eliminates the need to install expensive heat sinks. Xilinx also offers wireless IP to increase the efficiency of the power amplifier, which helps the design team further reduce the power consumption of small cell sites. Heterogeneous networks (HetNet) need to connect a large number of computers and devices with different operating systems and protocols. To this end, Xilinx has introduced an attractive portfolio of All Programmable devices. With maximum design flexibility, these products can meet HetNet's multi-standard and multi-band requirements with a single reconfigurable device. Whether you are designing a small cell or a traditional macrocell architecture, you can find the right Xilinx device. Xilinx's Zynq SoC devices offer higher system integration than any other device, making them ideal for small cellular HetNet systems. The dual-core ARM® CortexTM-A9 processor handles tasks in real time. One of the Cortex-A9 processors runs the real-time operating system and is responsible for handling L1 control tasks, while the other Cortex-A9 runs some or all of the higher layer functions. Heavy-duty user layer processing tasks are best done in hardware. Combining Xilinx's richest LTE baseband feature set with multi-core SoCs, the integrated 7 Series FPGA architecture delivers superior real-time performance at lower power. The FPGA architecture can also be used to accelerate the L2 user layer functionality, thereby reducing the load on the ARM processor, giving designers the flexibility to accelerate the hardware in the architecture to improve higher-level performance. The architecture also allows for integrated digital up-conversion and down-conversion (DUC/DDC), optional crest factor suppression (CFR), and digital front-end (DFE) functions such as digital pre-distortion (DPD). This high level of integration further reduces power consumption and helps reduce the overall end-to-end delay problem that is important in LTE base station design. Flexibility of Small Cell Base Stations Xilinx offers a Zynq SoC-based LTE small cell base station reference design for use with the Xilinx LTE baseband. Of course, customers can also integrate their own LET baseband. In addition, Xilinx offers comprehensive and comprehensive software solutions including LTE protocol stack, RAN security, backhaul IPSec, timing and synchronization, and Robust Header Compression (RoHC). The Zynq SoC supports the PCIe® protocol, enabling designers to easily integrate Wi-Fi functionality into SoC-based LET small cell base station designs. The Zynq SoC's high-performance processing capabilities and I/O make it ideal for high-performance small cell base station designs with integrated wireless backhaul. In addition, support for JESD204B enables SoC-based LET small cell base stations to easily connect to any industry-leading RF transceiver. For low- and medium-capacity small cell base stations, Xilinx uses Zynq SoC to implement a highly integrated solution with an integrated physical layer. The physical layer includes a radio + L1 baseband implemented in programmable logic (PL), and a higher layer protocol stack, backhaul transmission management, and physical layer timing and control implemented in a processing system (PS). Programmable logic also provides hardware acceleration for some higher-level functions to maximize capacity (an important factor in distance from competing products). The Zynq SoC family is available in a single-chip implementation for a variety of deployment scenarios. Considering the processing power of the current Zynq SoC series, for high-capacity small cell base stations, Xilinx recommends implementing a radio + L1 baseband in programmable logic to implement timing and control in the processing system. A secondary processor can be used to handle higher layer protocol stack and backhaul transport management tasks. The top image in Figure 1 is a typical 2X2 (2T2R) LTE small cell base station design. A typical bill of materials (BOM) for such designs typically consists of three chips: a multicore SoC, an ASSP (for a digital front end), and a small FPGA (for the remaining logic and memory). The following figure concentrates these chips in a single Zynq SoC device (such as the Z-7045), where the dual-core ARM Cortex-A9 runs the LTE L2/L3 protocol stack. LTE L1 is integrated into the FPGA fabric and provides hardware acceleration for L2 to share processing tasks such as IPSec, encryption and RoHC. The FPGA architecture also includes digital front ends (DPD, DUC, DDC, CFR). The single-chip design not only reduces inter-chip latency, achieves optimal packet processing, but also reduces material cost by 25%, system performance by doubling, and total power consumption by 35%. LTE small cell base station design requires low cost, low power consumption, high integration and high reliability. Total integration, scalability and flexibility are key to achieving these goals. With a dual-core ARM processor subsystem, high system performance and low-power programmable logic, the Zynq-7000 All Programmable SoC is a low-cost solution for today's and tomorrow's small cell base station needs. Braided Sleeve,Braided Cable Sleeve,Expandable Braided Sleeving,Braided Wire Sleeve Shenzhen Huiyunhai Tech.Co., Ltd. , https://www.cablesleevefactory.com

Zynq SoC's high-performance programmable logic and ARM processors enable customers to create designs that meet the ever-increasing transmission bandwidth requirements of today's and next-generation wireless devices. The design team can implement the protocol stack in the Zynq SoC processing system and observe its operation. If it is too slow, the Vivado® Design Suite High Level Synthesis (HLS) tool can be used to convert the code to Verilog or VHDL format for operation in Zynq SoC programmable logic. This can improve the overall system performance by increasing the speed of some feature code by a factor of 700 while freeing the processor to perform other tasks faster.