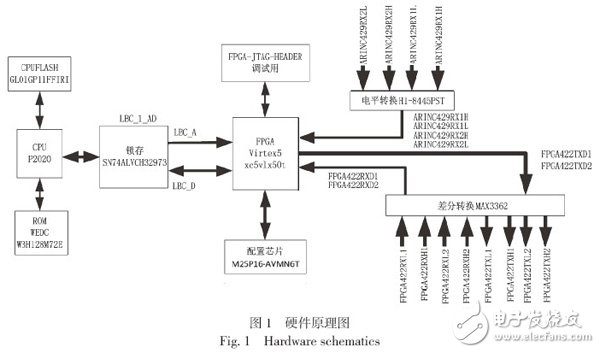

Abstract : This article uses workbench as the platform, vxworks as the operating system, chipscope as the analysis tool, introduces the complete ARINC429 protocol and 422 protocol FPGA hardware debugging, finds the problems that cannot be found by modelsim simulation through hardware debugging and analyzes the problem solving problem. Complete the design and implementation of multi-channel airborne bus transceivers. In the avionics integration system, fast and efficient data transmission has a great impact on the performance of the entire avionics system. Therefore, the data bus is called the skeleton of the modern avionics system, and the integrated multi-channel ARINC429 is designed by using FPGA technology. ] and 422 [4] channel communication chip, can effectively improve the processing power and integration of the data communication module, reduce costs, this article is based on verilog language, through ISE programming, modelsim simulation, simulation after error-free comprehensive implementation, with impact Write the bit file to the FPGA, perform hardware debugging, and analyze with chipscope. For more convenient debugging, build the driver with the workbench as the platform. The 429 protocol and the 422 protocol are very mature, so this paper mainly introduces the implementation of multi-channel airborne bus transceiver from the perspective of hardware debugging. In many cases, we need a board with both 429 [2-3] and 422 data transfer functions, so we set up 429 logic and 422 logic [6] under one module, assigning 429 logic and 422 logic differently. The address space controls the chip select signals of the 429 and 422 protocols through different address spaces, while the LOCALBUS data is bidirectional data, and the 429 and 422 data are unidirectional data, so a bidirectional buffer is needed to implement unidirectional data and bidirectional data. The conversion between. The protocol part is very mature and will not be repeated here. 2.1 Prototype Verification Board Principle The board name we use is: MFD-GPM1018. The design principle is shown in Figure 1: The CPU controls the writing and reading of the FPGA data. The data received by the FPGA through 429 or 422 is converted by the CPU after being converted according to the corresponding protocol. The CPU provides the data to be sent by the FPGA and configures the register through Localbus. The data read by the CPU is converted into a separate address signal and data signal by the LBC-1-AD00-07 to the latch to address and data according to certain control rules. LBC-1-AD00——07 indicates that the moment when the address signal is a data signal. The ROM stores the intermediate data path during the cpu operation. The H1-8445 level shifting converts the 429 data level from the level required by the bus bus to the 3.3V required by the FPGA. ASP105885-01 is a connector that connects 429, 422 data to the GPM debug version for hardware debugging. The MAX3362 converts serial data into a differential form. The M25P16-AVMN6T is a configuration chip for the FPGA. After the bit file is loaded into the FPGA through the JTAG interface, the bit file can be directly loaded into the FPGA without reloading after the next power-on. 2.2 Hardware debugging process In the Workbench development platform vxworks [3] operating system, first connect the serial network port from the debugging board to the PC, create a new HyperTerminal, select the communication rate is 115200, the others are the default values, the network port downloads the operating system to In the cpu, the serial port is used to control the cpu. After the serial port is connected, connect the JTAG interface. (JTAG cable connects the USB download cable to the PC), set the power supply voltage to 28V, then power on, and pass the voltage on the debug board. The converter is converted to 5V for use by the FPGA board. After power-on, the .bit file is downloaded to the FPGA through IMPACT. This type of configuration is lost when it is powered off. It needs to be re-downloaded after power-on, and the HyperTerminal is opened to establish a serial port connection. At this point, the vxworks operating system will start automatically. Enter some commands to control the cpu under this operating system. The common ones are read (d) and write (m) commands, and open chipscope for debugging. In order to fully verify the correctness of the logic function: we perform the internal loopback test separately, that is, realize the self-receiving and self-sufficiency in the logic, and then perform the external loopback test, connect the sending interface on the board to the receiving interface, realize the loopback transceiver, and the test is correct. After the external test, the 429 protocol is tested with the 429 simulation card, and the 422 protocol is tested with the serial debugging tool. 2.2.1 429 test 429 emulation card BUStools /ARINC v3.20 simulation verification: 3) After the setting is completed, click run to stop sending and click stop. The data received by the HyperTerminal reads the received data in accordance with the transmitted data, and the test is correct. 2.2.2 422 Testing with Serial Debugging Tools Low Voltage SWA Armored Cable,SWA Armored Cable,Copper Sheathed Power Cable,Low Voltage XLPE Power Cable Ruitian Cable CO.,LTD. , https://www.hbruitiancable.com

The 429 emulation card sends 429 differential data, which is received by the FPGA to determine whether the received data is transmitted data, so as to detect the correctness of the receiving logic.

1) TX setup : Set the transmission channel, baud rate, parity

2) DEFINE : ADD new message Add the transmission channel, we need TXD1, TXD2, set the transmission data parameters: data - BIN set 32-9 data, the first 8 data is set by Label, Label is a 233 data type, 2 refers It is 2 bits. For example, if it is set to 256, it is 10101110. The data mapped to the transmission is 0111 0101, which is 0x75. The highest bit is the parity bit, which is automatically generated during transmission.

The sending port and receiving port of 422 are connected to the PC through 232. The PC sends a string of data through the serial port debugging tool. After receiving the data through 232 to 422, the received data is printed in the HyperTerminal, and the receiving is correct. The driver 422 is sent to send a string of data, and the transmitted data is seen through the serial port debugging tool through the 232 to the PC, and the sent data is detected to be correct. The key point in the debugging process is that the baud rate of the transmit and receive ports should be set consistently.