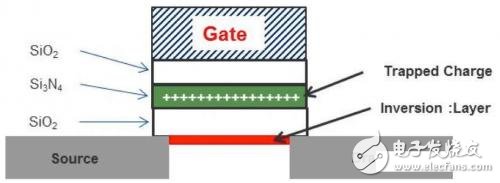

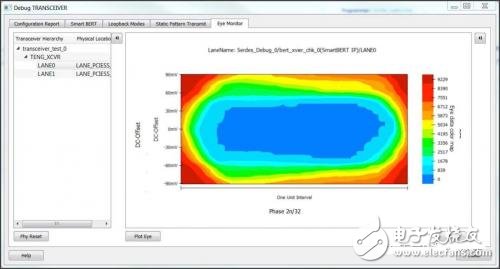

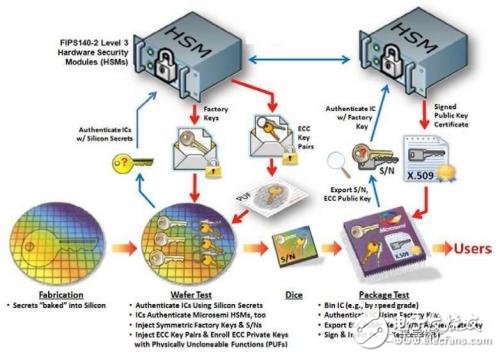

Multiple trends are driving FPGAs to two very different development paths. On the first road, FPGAs are constantly optimized to accelerate data center workloads. The data center is the next "Holy Grail" for large vendors. In another development path, there are the traditional FPGA network market, cellular base stations, defense, commercial aviation, industry 4.0 and medical. In these application areas, many engineers think they are being abandoned. The development challenges they face are very different from the data center focus of large vendors. Designers face increasingly difficult balance behaviors because they try to achieve low power and low cost without sacrificing performance and security. To achieve this balance, you need to look at FPGAs in new ways, with new process technology choices, structural designs, transceiver strategies, and built-in security measures. This gave birth to a new class of mid-size FPGAs that provided new capabilities for traditional FPGA developers. One way to reduce power consumption while optimizing the cost of mid-range FPGAs is to use new process technologies. For example, Silicon-Oxide-Nitride-Silicon (SONOS) non-volatile (NV) technology is used on 28nm technology nodes with lower power consumption advantages compared to SRAM-based FPGAs on the same or smaller nodes. . Previous generation nonvolatile FPGAs using 65nm and above floating gate NV technology are more expensive than SONOS. Given that floating gate technology requires 17.5 V to program a large charge pump that consumes a lot of chip area, SONOS technology only requires 7.5 V programming, so the charge pump can be smaller. This technology can reduce the chip size and help provide more cost-effective devices. SONOS technology achieves these advantages by using a single polysilicon transistor stack (see FIG. 1) having a non-conductive nitride dielectric layer (Si3N4) as a charge storage unit. With this method, only a very small amount of charge will be lost near any defects that may be present in the bottom oxide. Since the stored charge is immovable in the insulating nitride layer, most of the stored charge remains intact and intact. Thinner bottom oxide can be used compared to floating gate technology, and can be programmed with a lower programming voltage (~7.5 V) and a smaller charge pump. The use of SONOS requires fewer transistors than SRAM memory cells. Figure 1: SONOS technology. (Source: Microsemi) SONOS technology improves reliability by using push-pull cells containing N-channel and P-channel NV devices. The NV device is not in the data path and is only used to control the standard transistors used as data path switches. This provides a great functional advantage because any change in the threshold voltage (Vt) of the NV device does not change the switch conductance. The way the device interacts acts as a built-in quasi-redundancy that prevents the product from deteriorating during use. Power consumption will also be reduced. First, the SONOS NV FPGA configuration unit enables two different programmable “configured†states to control the FPGA data signal path and optimizes switching devices on off and on to provide much lower leakage than standard transistors. Second, SONOS technology can place the device in a state where the supply voltage is turned off to the configuration memory in the FPGA logic block, while saving the user's state in the low-power latches. This reduces the standby power consumption by about two-thirds. SONOS also has two important advantages. The first is the "on-the-fly" function: because the FPGA logic configuration unit maintains its state after a power failure, there is no need to reload the FPGA design code when the power returns, nor does it require an external boot PROM. Second, unlike configuration memories in SRAM-based FPGAs, the device can flip state due to neutron bombardment and the SONOS device's FPGA logic configuration is not affected by the SEU. The SONOS NV charge is stored in the nitride dielectric and is not susceptible to charge loss due to neutron bombardment. Another way to improve the performance of mid-range FPGAs is to change the programmable logic structure. This allows the device to meet mainstream performance requirements, while the static power consumption is only one-tenth of the SRAM FPGA and half of the total power consumption. Power consumption and performance need to be balanced. For example, a 6-input LUT can provide some speed advantages, but a 4-input LUT is a better choice for power and cost-optimized FPGAs in modern process technologies. At the same time, as the process technology progressed from 65 nm to 28 nm and above, due to the poor scaling of the metal lines and via resistance, the delay of the wiring has become the dominant factor of logic delay. Broadening metal lines will increase chip area and cost. Therefore, with each successive generation of process technology, the inter-cluster delay will become the primary issue of the critical path, and the speed advantage of the 6-input LUT will be reduced. Ensuring fast direct connections between adjacent LUTs can reduce intra-cluster latencies, especially with advanced synthesis and layout algorithms. Some logic functions (such as the MUX tree) can benefit from direct connections. For best results, the FPGA family's power performance trade-offs should be carefully optimized so that the core logic supply voltage is slightly lower than the nominal voltage of its manufacturing process. In a 28 nm SONOS device, this means optimizing the 1.0V core logic supply voltage, and the option of using the full 1.05 V supply when additional speed is needed. The final piece of the FPGA architecture is the math module, which should support 18-bit multiply-accumulate operations. By providing a pre-adder with a full 19-bit cascade of results and input values, and by ensuring that the math module supports accurate 9-bit operations, including the 9&9;9 dot product mode. The latter is very suitable for image processing and convolutional neural networks (CNN). Transceivers play an important role in optimizing FPGA costs, power consumption, and performance requirements. Many applications require up to 24 high-speed, full-duplex transceiver channels. They also need a SerDes transceiver that can support baud rates from 250 Mbps to 12.7 Gbps to cover the full range of SDI, up to 10Gbps Ethernet, JESD204B converters, and other applications. One of the major advantages of optimizing transceivers is to reduce the performance of higher-speed SerDes tuned from high-end FPGAs because it consumes much less power at all baud rates than the degraded SerDes method. Multiple architectural choices can help reduce FPGA transceiver power consumption, from using transceivers in half-rate architectures to using highly shared transport PLL architectures. Ideally, FPGAs should have 1 to 6 quad transceivers and up to 24 SerDes channels. Many equalization functions allow longer distances and use low-cost materials in printed circuit boards and backplanes. Special phase-locked loop (PLL) features provide users with more flexibility, from more flexible clock and baud rate selection to simplified radial-emission requirements, and higher bandwidth options. Debugging and testing are also important, including the availability of built-in pseudo-random binary sequence (PRBS) generators and detectors and IEEE 1149.6 "AC JTAG" supporting non-DC-coupled signals. Including a built-in eye monitor with debug software support, designers can debug SerDes without an oscilloscope. One can optimize the DFE and CTLE parameters in real time and call the ideal settings for the end product (see Figure 2). Fig. 2: SerDes eye monitor intelligent debugging software At present, there are many threats to the security of the design. Everything from the user's design IP to the manufacturing process can be affected. Key security technologies and capabilities include trusted hardware roots, powerful encryption technologies, and top-level key management at each stage, as well as built-in passive and active countermeasures to prevent tampering. Figure 3 shows the best implementation of a secure FPGA configuration using a unique serial number, key, and X.509 public key certificate. Figure 3: Device Certificate Chain of Trust With these components, design and data security issues can be solved. Design security requires that the FPGA use manufacturer-provided keys and certificates, as well as other technologies (from patented differential power analysis (DPA) countermeasures to technologies that prevent side-channel attacks) to protect the user's IP. Another way to increase design security is to use physical Unclonable Function (PUF) technology to generate hardware intrinsic keys. Data security requires the use of a cryptographic processor dedicated to core NIST-certified FPGA users to implement many of the most common encryption algorithms, such as AES, SHA 2, ECC, RSA, and DH, and include an encryption-level TRNG. Compared to adding accelerators to the FPGA fabric, user cryptographic processors are suitable for many applications, thereby reducing costs (area, power consumption, and other related). There is an increasing market demand for medium-size FPGAs that require cost optimization. In the communications, defense, and industrial markets, density densities of up to 500K logic units (LEs) require a significant reduction in power density. A new roadmap has emerged that combines new process technologies and structural designs with key transceiver changes and security features to enable FPGAs to address the cost, power, performance, and security requirements of mainstream applications while providing All the advantages of volatile technology. Nomex Braided Sleeve,Nomex Braided Hose,Nomex Sleeving,Nomex Braided Sleeving Shenzhen Huiyunhai Tech.Co., Ltd. , https://www.cablesleevefactory.com