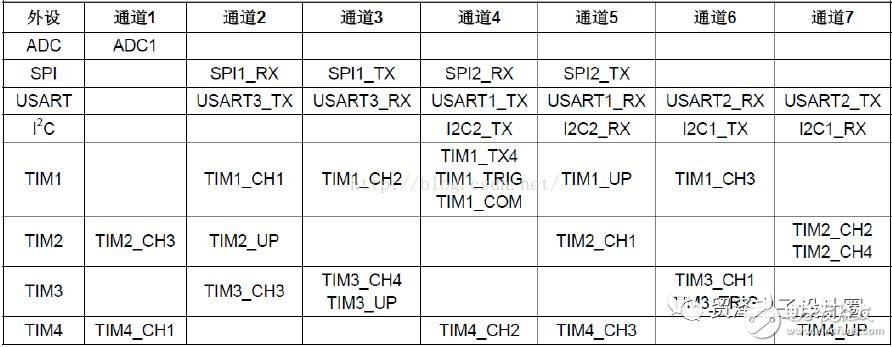

Yesterday evening on the STM32 serial DMA problem tangled for a long time, so this morning to write a blog to talk about my understanding of serial DMA transmission. 1. What is a serial DMA request; 2. Brief review of the serial port; 3. Serial DMA transmission process. 1. What is the serial port DMA request (Battleship STM32 development board) Before talking about this problem, briefly review the basic characteristics of DMA. First export the atomic brother's PPT content: DMA is called Direct Memory Access, which is direct memory access. DMA transfers copy data from one address space to another. When the CPU initializes this transfer action, the transfer action itself is implemented and completed by the DMA controller. STM32 has two DMA controllers (DMA2 only exists in high-capacity products), DMA1 has 7 channels, DMA2 has 5 channels, and each channel is dedicated to manage access requests from one or more peripherals to memory. . There is also an arbiter to coordinate the priority of each DMA request. Role: for the CPU to reduce the burden! Above picture DMA channels DMA requests from peripherals (TIMx, ADCx, SPIx, I2Cx, and USARTx) are either logically OR input to the DMA controller, which means that only one request can be active at a time (at the same time, only one of them can be used) One, the other channels are similar). The DMA request of the peripheral can be turned on or off independently by setting the control bits in the corresponding peripheral registers. See the definition of the serial port DMA request here: first give an example: For example, I want to use the serial port to send data to the PC. The general practice is that the CPU writes data to the serial port through the APB1/APB2 bus, and then sends the serial port; or the CPU passes The bus fetches (reads) data from the serial port; if the CPU handles a lot of tasks at this time, it will consume CPU processing time. And if we use DMA to transfer data, it will be very fast, DMA will copy data from one address space to another through its own specific channel, and does not require CPU intervention. Therefore, the definition of the serial port DMA request is: the serial port to send/receive data will request DMA to complete the writing and reading of the data. (Note that this sentence is only for this article!) 2, serial port brief review (library function) Here to share a post about printf redirection and semi-host mode understanding: Http://?mod=viewthread&tid=44609&highlight=printf Here is a brief review of the knowledge points of the battleship STM32 serial port. For example: I want to use a PC to send data to the STM32 serial port, and then the STM32 receives the data and returns it to the PC as it is (displayed in the serial debugging assistant). Idea: First, we will configure the serial port receiving interrupt in the serial port initialization function. When your PC sends data to the serial port, the serial port will generate a receiving interrupt. In the interrupt service function, it will judge whether the receiving is completed or not. If the receiving is completed, the receiving status will be received. The receive completion flag of the register is set to 1. Here is the role of receiving interrupts. . Then in the main function, we continuously detect the reception completion flag of the receive status register, and see that it has not been received. If the reception is completed, the received data will be sent to the USART_DR register of the serial port through the for loop (the serial port will be sent automatically when writing data to this register). Therefore, the data that we send to the serial port through the PC will be sent back by the STM32 through the serial port, which is displayed in the serial port debugging assistant. 3, serial DMA transmission process (library function) Battleship experiment: Control DMA transmission by pressing KEY0. Each time KEY0 is pressed, DMA transfers data to USART1, and then displays progress information on TFTLCD module. This is not difficult to understand now. Starting from the main function, first we open a section of 5200 in the SRAM of the STM32 (the larger the number, the slower the DMA transfer, and the faster the reverse) the space of the SendBuff[], as our memory (memory), the storage to the peripherals ( USART1) sent data. Then we fill the contents of TEXT_TO_SEND[] in SendBuff[]. Here the algorithm written by the warship to SendBuff[] is very clever and should be learned; Now SendBuff[] is full of data to be sent to the serial port. At this time, we also need to check if KEY0 is pressed. If it is pressed, it will pass two functions: 1. Enable serial port transmission (in the STM32 library function stm32f10x_usart.c, configure the DMA enable bit DMAT in USART_CR3); 2. Enable DMA1 channel 4 and start the transfer (in dam.c, finally call DMA_Cmd() in stm32f10x_dma.c; function to enable the channel). In addition to the previous (in this article) initialization of the DMA parameters (initialization of memory and peripheral base address, etc.), a transfer can be initiated. Transmission time problem: Transmission time is closely related to baud rate. For example, the baud rate is 9600, which means that the rate of sending or receiving every second is 9600 bit/s, 8bit=1 Byte (byte), so when the baud rate is 9600, the serial port transmission rate is 1200 bytes per second. The memory (memory) space we applied above is 5200 bytes, so the serial port needs to transfer the content content of this size, which is expected to be 5200/1200 for about 4 seconds. . .

Kadena (KDA) is a hybrid blockchain network and smart contract platform that aims to unite public applications, private blockchains, and other interoperable chains in one place, driving traffic to the high-bandwidth computer at the heart of the Kadena public chain. Kadena`s mining algorithm is Blake2S, which supports ASIC mining.

Kadena is a blockchain network and smart contract token aiming to bring together both public applications and private blockchain.

A few changes have come into Kadena mining. A proof of work blockchain uses PACT to create smart contracts in the hidden gen. Therefore you need to know the following before mining Kadena. PACT is an intelligent contract language serving the needs of the blockchain community. Kda Miner,Antminer Ka3 166Th,Bitmain Antminer Ka3 166Th,Antminer Bitmain Ka3 Shenzhen YLHM Technology Co., Ltd. , https://www.sggminer.com

The coin solves various problems that prevent blockchain adoption on a bigger scale. The protocol enables businesses and developers to make transactions and share information across many networks.

The Coin is actually on the grid to reduce users` experience in the network. Ethereum users experience a lot of network congestion which results in high gas fees.

1.You Need an Excellent Mining Hardware

To mine efficiently, you will require suitable mining hardware. Kadena uses ASIC miners. But, unfortunately for Kadena miners, CPUs and GPUs are not usable. Furthermore, ASIC mining receives support from the Blake2S algorithm.

2.Make Sure You Have a Kadena Wallet Address

You will need a Kadena wallet address to receive and monitor your profit. F2pool also makes the distribution of the revenues to every user daily at 2KDA. The Kadena node wallet is a perfect wallet where you can receive your mined KDA. all you need to do is install it, click receive, and have a new wallet address.

You will need to configure your Asic Miner to a mining pool server for your hashrate and profit to be recorded and monitored.

3.Start Mining

After all the setting is done, your miner will be ready to work. Make sure you enter your wallet address and click on the go button to receive your revenue.