First, the bus overview Computer system is based on the microprocessor, each device must be connected to the microprocessor, and must work in coordination, so the concept of the bus is introduced in the microprocessor, the devices share the bus, any time only There can be one device to send data (multiple devices can receive data at the same time). Wire harnesses are commonly used in the electronics industry, the automotive industry, in the manufacture of construction machinery and industrial equipment, as well as in the manufacture of white goods such as washing machines and dryers, refrigerators, and other household appliances.A industrial wire harness is typically designed to simplify the manufacture of a larger component, and is designed based on the geometric and electrical requirements of the equipment it is to be installed in. Industrial Cable Harness,Mechanical Cable Assembly,Industrial Cable Harness,Mechanical Cable Assembly,Accessories Service ETOP WIREHARNESS LIMITED , https://www.oemwireharness.com

The bus of the computer is divided into three types: control bus, address bus and data bus. The data bus is used to transfer data, the control bus is used to transmit control signals, and the address bus is used to select memory cells or peripherals.

Second, the three-bus structure of the single chip microcomputer

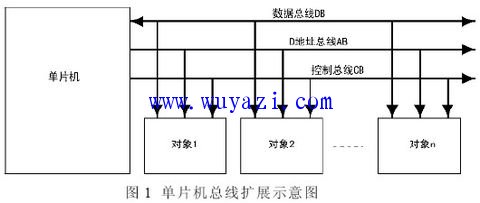

The 51 series MCU has a complete bus interface timing, which can extend the control object, and its direct addressing capability reaches 64k (2 to the 16th power). In the bus mode, different objects share the bus, independently address and time-multiplex the bus, and the CPU selects the accessed object through the address to complete the information transfer with each object.

The three-bus extension of the MCU is shown in Figure 1.

1, the data bus

The data bus of 51 MCU is P0 port, P0 port is bidirectional data channel, CPU sends and reads back data from P0 port.

2, the address bus

The address bus of the 51 series MCU is 16 bits.

In order to save the chip pins, the P0 port multiplexing mode is adopted. In addition to being the data bus, under the ALE signal timing matching, the external data latch is used to send the lower 8-bit address from the P0 port in the first half cycle of the bus access. The half cycle sends 8-bit data from port P0.

The upper 8-bit address is sent through the P2 port.

3, control bus

The control bus of the 51 series MCU includes the read control signal P3.7 and the write control signal P3.6, which are respectively used as the enable signals for data read and data write in the bus mode.

Third, the microcontroller bus timing analysis

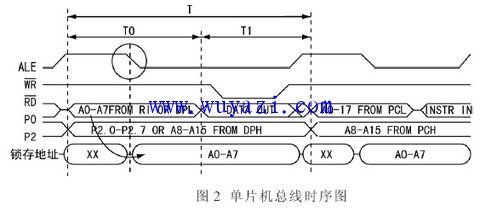

51 MCU bus timing is shown in Figure 2.

As can be seen from Figure 2, the completion of a bus (read and write) operation cycle is T, P0 port time division multiplexing, during T0, P0 port sends the lower 8 bit address, completes the data latch on the falling edge of ALE, and sends out Low 8-bit address signal. During T1, port P0 is used as a data bus to send or read data. The data read and write operations are completed during the low period of the read and write control signals.

It should be noted that during the period when the control signal (read and write signals) is valid, P2 port sends the upper 8-bit address and cooperates with the lower 8-bit address of the data latch output to realize the 16-bit address bus, that is, within the 64kB range. site.

Since the CPU cannot perform both read and write operations, the read and write signals cannot be valid at the same time.

Fourth, common microcontroller addressing circuit

1, simple address expansion

The P2 port of the MCU can be directly used as the high 8-bit address bus. In some simple system circuits, the P2 port is directly used for addressing.

The following uses the data buffer 74LS273 to drive the digital display as an example to analyze the design of the static digital display circuit driven by the P2 port addressing.

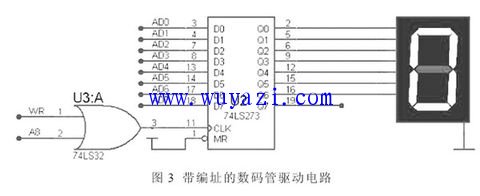

An LED digital display unit circuit is shown in Figure 3.

WR and A8 (P2.0) provide a clock signal of 74LS273. When the "MOVX @DPTR,A" instruction is executed, the address information is determined by the DPTR register, and a valid write signal WR will appear, only when the address A8 is satisfied. When 0â€, the write signal can be used as the clock signal input of 74LS273 to complete the data latch.

P2 port is an 8-bit address line of A8~A15, which can be easily extended to 8 LED digital tubes. The WR signal is connected with A8~A15 respectively or in relation to each other. Each address line is active low, which can realize 8 Effective address.

The scheme is simple, but the number of effective addresses is too small, which is not suitable for complex system design.

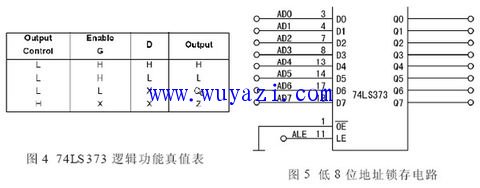

2, the low 8-bit address latch The usual design circuit is to use the 8D latch 74LS373 to achieve address latching, 74HC573 with the same logic function, but the pin layout is not the same, using 74HC573 wiring is easier.

The 74LS373 truth table is shown in Figure 4.

When the output allows OE to be L and the control enable LE to be H, the output is in the following state;

When OE is L and LE is L, the output is held.

The address latch circuit is shown in Figure 5. OE is grounded, and the ALE pin of the LE connected to the microcontroller will generate the lower 8-bit address signal that satisfies the timing.

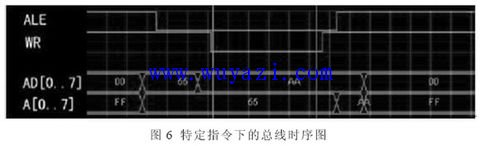

Execute the following three instructions to get the timing diagram shown in Figure 6.

MOV DPTR, # 0FF55H; The lower 8 bit address is 55H

MOV A, # 0AAH; Data to be sent 0AAH→A (55H inversion)

MOVX, @DPTR, A; 0AAH in A will send an address of 0FF55H.

As can be seen from Figure 6, the P0 port first sends 55H, the address latch is implemented on the falling edge of ALE, and then the data 0AAH is sent. During the WR active (low level), the latch outputs the lower 8-bit address 55H, and the P0 port sends the data. 0AAH.

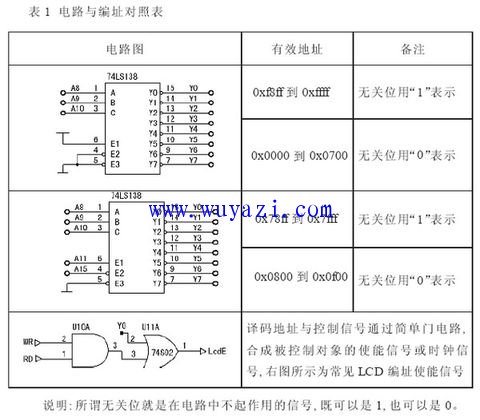

3. Complex address interface circuit with decoder Theoretically, the upper 8-bit address line can generate 256 effective addresses. How to implement address "expansion"? The address extension is accurately described as address decoding. For example, three address lines can be decoded. It is 8 addresses and 4 are decoded into 16 effective addresses. Here, the 3-8 decoder is selected to implement address decoding. The circuit diagram and corresponding addressing are shown in Table 1.

V. Single-chip microcomputer bus address circuit example Single-chip microcomputer system with bus expansion interface, including external 32k RAM expansion, LCD1602 interface, input and output port.

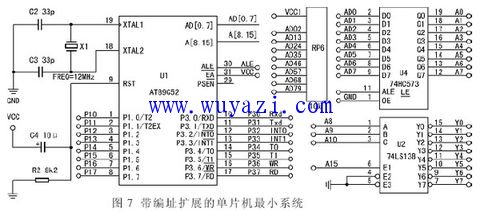

The minimum system circuit of the MCU with addressing extension is shown in Figure 7.

Use 74HC573 to latch the lower 8-bit address; 74138 to achieve 8 address expansion, 74138 A, B, C are connected to A8 ~ A10, E1 is connected to A15, E2, E3 is always valid, get 0F8FFH to 0FFFFH8 addresses (don't care bit 1 Indicates) or 8000H to 8700H (don't care bits are represented by 0).

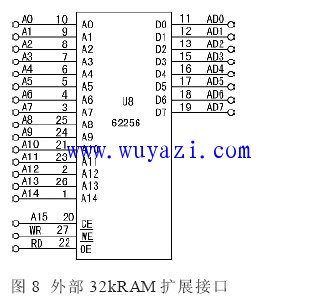

The 32k RAM interface is shown in Figure 8.

D0~D7 are connected to data bus port P0, address line A0~A14 is connected to the lower address of the address bus of the MCU, and the address line of the MCU is connected to the RAM chip select signal, which is active low, so the RAM address is allocated from 0000H to 7FFFH, and 74138 is decoded. The addresses do not conflict.

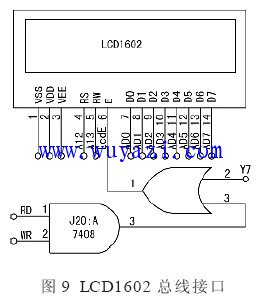

The LCD1602 interface circuit is shown in Figure 9.

RS and RW are connected to A12 and A13 respectively, and the enable signal is addressed to Y7, so the four drive addresses (data read/write and command read/write) of the LCD are 0CFFFH to 0FFFFH (don't care bit is 1) or 8700H to 0B700H (don't care bits). Is 0).

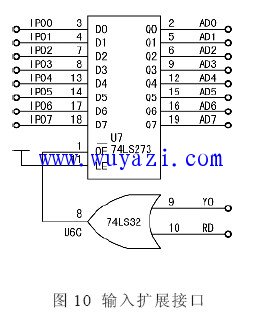

In some cases, the MCU pins are not enough, and they need to be expanded. The input port expansion circuit is shown in Figure 10.

Using the high-impedance function of the 74HC573 ( 74LS373), its output Q0 ~ Q7 is connected to the P0 port. In the bus address read operation, the input InPORT data can be read into the accumulator of the microcontroller, the address is 0F8FFH or 8000H.

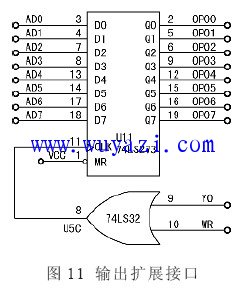

The output port expansion circuit is shown in Figure 11.

Using the 74LS273 data latch function, the data in the microcontroller accumulator can be written to the 273 latched output at address 0F8FFH or 8000H while the bus address write operation is satisfied. Since the control bus used is different, the address can be shared with the input.

6. Conclusion Bus expansion is a technology that must be mastered in designing a microcontroller control circuit. A large number of special function ICs support bus interfaces, such as ADC0809, TLC7528, and DDS device AD9851.

The main point of the bus interface is that under strict control timing, the bus is time-multiplexed to achieve complex system design.